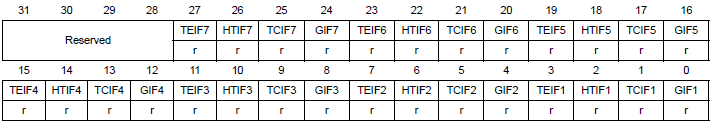

DMA_ISR - регистр состояния прерываний DMA.

Содержит флаги событий, связанных с прерываниями DMA.

Биты 31:28. Зарезервированы, должны быть сброшены.

Биты 27, 23, 19, 15, 11, 7, 3 TEIFx (TEIF7…TEIF1). Флаг ошибки передачи канала с номером x. Признак устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

- 0: передача прошла без ошибок

- 1: произошла ошибка на канале x.

Биты 26, 22, 18, 14, 10, 6, 2 HTIFx (HTIF7… HTIF1). Флаг завершения передачи половины данных канала с номером x. Признак устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

- 0: передача половины данных не закончена

- 1: передача половины данных завершена.

Биты 25, 21, 17, 13, 9, 5, 1 TCIFx (TCIF7… TCIF1). Флаг завершения передачи канала с номером x. Признак устанавливается аппаратно. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

- 0: передача данных не закончена

- 1: передача данных завершена.

Биты 24, 20, 16, 12, 8, 4, 0 GIFx (GIF7… GIF1). Флаг глобального прерывания канала с номером x. Признак устанавливается аппаратно при появлении любого из событий TE, HT, TC. Сбрасывается программно записью 1 в соответствующий бит регистра DMA_IFCR.

- 0: не произошло ни одного из событий TE, HT или TC.

- 1: произошло хотя бы одно событие TE, HT или TC.

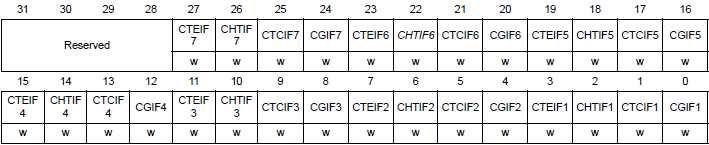

DMA_IFCR – регистр сброса флагов прерываний DMA.

Предназначен для программного сброса флагов событий в регистре DMA_ISR. Запись 1 в соответствующий бит сбрасывает признак события. Запись 0 игнорируется.

Биты 31:28. Зарезервированы, должны быть сброшены.

Биты 27, 23, 19, 15, 11, 7, 3 CTEIFx (CTEIF7…CTEIF1). Сброс флага ошибки передачи канала с номером x.

- 1: Сброс флага TEIFx в регистре DMA_ISR.

Биты 26, 22, 18, 14, 10, 6, 2 CHTIFx (CHTIF7… CHTIF1). Сброс флага завершения передачи половины данных канала с номером x.

- 1: Сброс флага HTIFx в регистре DMA_ISR.

Биты 25, 21, 17, 13, 9, 5, 1 CTCIFx (CTCIF7… CTCIF1). Сброс флага завершения передачи канала с номером x.

- 1: Сброс флага TCIFx в регистре DMA_ISR.

Биты 24, 20, 16, 12, 8, 4, 0 CGIFx (CGIF7… CGIF1). Сброс флага глобального прерывания канала с номером x.

- 1: Сброс всех флагов GIFx, TEIFx, HTIFx и TCIFx в регистре DMA_ISR.

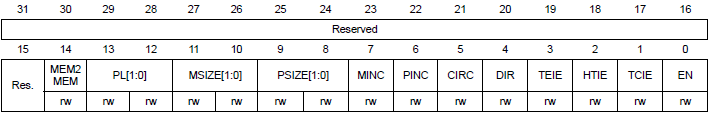

DMA_CCRx (DMA_CCR7… DMA_CCR1) – регистр конфигурации канала номер x.

У каждого канала свой отдельный регистр, который задает режим работы канала DMA.

Биты 31:15. Зарезервированы, должны быть сброшены.

Бит 14 MEM2MEM. Разрешение режима “Memory to memory” (пересылка данных из памяти в память).

- 0: Режим “Memory to memory” отключен.

- 1: Режим “Memory to memory” включен.

Биты 13:12 PL[1:0]. Уровень приоритета канала.

- 00: низкий;

- 01: средний;

- 10: высокий;

- 11: очень высокий.

Биты 11:10 MSIZE[1:0]. Размер элемента данных памяти. Поле определяет размер элемента данных, который записывается в память или считывается из нее за одну транзакцию.

- 00: 8 бит (байт);

- 01: 16 бит (полуслово);

- 10: 32 бита (слово);

- 11: Не используется.

Биты 9:8 PSIZE [1:0]. Размер элемента данных периферийного устройства. Поле определяет размер элемента данных, который записывается в периферийное устройство или считывается из него за одну транзакцию.

- 00: 8 бит (байт);

- 01: 16 бит (полуслово);

- 10: 32 бита (слово);

- 11: не используется.

Бит 7 MINC. Разрешение режима инкрементирования адреса памяти.

- 0: Инкрементирование адреса запрещено.

- 1: Инкрементирование адреса включено.

Бит 6 PINC. Разрешение режима инкрементирования адреса периферийного устройства.

- 0: Инкрементирование адреса запрещено.

- 1: Инкрементирование адреса включено.

Бит 5 CIRC. Разрешение циклического режима.

- 0: Циклический режим отключен.

- 1: Циклический режим включен.

Бит 4 DIR. Направление передачи данных.

- 0: Чтение данных из периферийного устройства.

- 1: Чтение данных из памяти.

Бит 3 TEIE. Разрешение прерываний при появлении ошибок передачи.

- 0: При появлении ошибок передачи прерывания не генерируются.

- 1: При появлении ошибок передачи генерируются прерывания.

Бит 2 HTIE. Разрешение прерываний при завершении передачи половины данных.

- 0: При завершении передачи половины данных прерывания не генерируются.

- 1: При завершении передачи половины данных генерируются прерывания.

Бит 1 TCIE. Разрешение прерываний при завершении передачи данных.

- 0: При завершении передачи данных прерывания не генерируются.

- 1: При завершении передачи данных генерируются прерывания.

Бит 0 EN. Разрешение работы канала.

- 0: Канал отключен.

- 1: Канал разрешен.

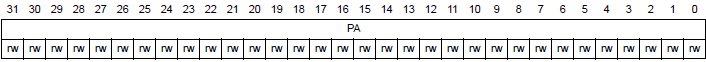

DMA_CPARx (DMA_CPAR7… DMA_CPAR1) – регистр адреса периферийного устройства канала номер x.

Биты 31:0 PA[31:0]. Базовый адрес регистра данных периферийного устройства. Доступ к периферийному устройству происходит с автоматическим выравниванием в зависимости от размера данных. Если размер элемента данных установлен 16 бит (PSIZE=01 ), то игнорируется младший бит адреса (PA[0]). Если задан размер данных 32 бита (PSIZE=10 ), то игнорируются два младших бита (PA[1:0]).

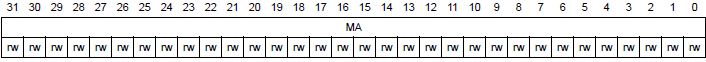

DMA_CMARx (DMA_CMAR7… DMA_CMAR1) – регистр адреса памяти канала номер x.

Биты 31:0 MA[31:0]. Базовый адрес памяти. Доступ к памяти происходит с автоматическим выравниванием в зависимости от размера данных. Если размер элемента данных установлен 16 бит (MSIZE=01 ), то игнорируется младший бит адреса (MA[0]). Если задан размер данных 32 бита (MSIZE=10 ), то игнорируются два младших бита (MA[1:0]).

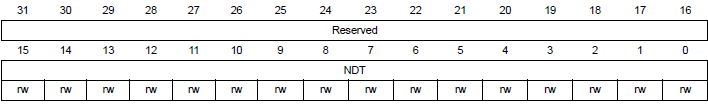

DMA_CNDTRx (DMA_CNDTR7… DMA_CNDTR1) – регистр количества данных передачи канала номер x.

Биты 31:16. Зарезервированы, должны быть сброшены.

Биты 15:0 NDT[15:0]. Количество данных для передачи (0 … 65535). Записывать в регистр можно только при отключенном канале. После включения, регистр становится доступным только для чтения и хранит оставшееся количество транзакций. Содержимое регистра уменьшается после каждой транзакции. При достижении значения регистра 0, передача останавливается. В циклическом режиме регистр автоматически перезагружается первоначальным значением, и передача данных продолжается.