По умолчанию состояние бита равное 1 означает разрешенный режим или событие. Не указанные биты – резервные, должны быть установлены в 0.

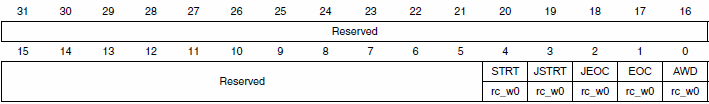

ADC_SR - регистр состояния АЦП.

Бит 4 STRT. Запуск регулярных каналов. Бит устанавливается аппаратно после запуска, сбрасывается программно.

Бит 3 JSTRT. Запуск инжектированных каналов. Бит устанавливается аппаратно после запуска, сбрасывается программно.

Бит 2 JEOC. Завершение преобразования всех каналов инжектированной группы. Бит устанавливается аппаратно, сбрасывается программно.

Бит 1 EOC. Завершение преобразования всех каналов инжектированной или регулярной групп. Бит устанавливается аппаратно, сбрасывается программно или чтением регистра ADC_DR.

Бит 0 AWD. Бит оконного компаратора. Устанавливается аппаратно при пересечении напряжением входного сигнала предельных значений, заданных в регистрах ADC_LTR и ADC_HTR. Сбрасывается программно.

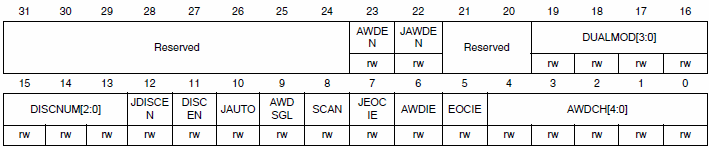

ADC_CR1 – регистр управления 1.

Бит 23 AWDEN. Разрешение оконного компаратора (analog watchdog) для регулярных каналов.

Бит 22. JAWDEN. Разрешение оконного компаратора (analog watchdog) для инжектированных каналов.

Биты 19:16 DUALMOD [3:0]. Режим совместной работы двух АЦП. Это поле есть только в АЦП 1.

- 0000: независимая работа АЦП

- 0001: комбинированный режим одновременного преобразования регулярной и инжектированной групп

- 0010: комбинированный режим одновременного преобразования регулярной группы и поочередного запуска

- 0011: комбинированный режим одновременного преобразования инжектированной группы и быстрого преобразования со смещением во времени

- 0100: комбинированный режим одновременного преобразования инжектированной группы и медленного преобразования со смещением во времени

- 0101: режим одновременного преобразования только инжектированной группы

- 0110: режим одновременного преобразования только регулярной группы

- 0111: режим быстрого преобразования со смещением во времени

- 1000: режим медленного преобразования со смещением во времени

- 1001: режим только поочередного запуска

Биты 15:13 DISCNUM [2:0]. Количество регулярных каналов в прерывистом режиме. Определяет сколько каналов надо опросить по приходу внешнего запуска.

- 000: 1 канал

- 0001: 2 канала

- . . . . . . . . . . .

- 111: 8 каналов

Бит 12 JDISCEN. Разрешение прерывистого режима для инжекционных каналов.

Бит 11 DISCEN. Разрешение прерывистого режима для регулярных каналов.

Бит 10 JAUTO. Разрешение автоматического преобразования для инжекционных каналов после преобразования регулярной группы.

Бит 9 AWDSGL. Режим работы оконного компаратора для всех (0) или для одного канала (1), заданного кодом в AWDCH[4:0].

Бит 8 SCAN. Разрешает режим сканирования каналов.

Бит 7 JEOCIE. Разрешение прерывания для инжекционных каналов.

Бит 6 AWDIE. Разрешение прерывания для оконного компаратора.

Бит 5 EOCIE. Разрешение прерывания по окончанию преобразований, для регулярных и инжекционных каналов.

Бит 4:0 AWDCH [4:0]. Выбор канала для оконного компаратора.

- 00000: канал 0

- 00001: канал 1

- . . . . . . . . . . . .

- 10001: канал 17

ADC_CR2 – регистр управления 2.

Бит 23 TSVREFE. Разрешение работы внутренних датчика температуры и ИОН. Бит присутствует только в АЦП 1.

Бит 22 SWSTART. Запуск преобразования регулярных каналов.

Бит 21 JSWSTART. Запуск преобразования инжекционных каналов.

Бит 20 EXTTRIG. Разрешение внешнего запуска преобразования для регулярных каналов.

Биты 19:17 EXTSEL [2:0]. Выбор источника запуска для регулярных каналов.

- 000: событие Timer 1 CC1

- 001: событие Timer 1 CC2

- 010: событие Timer 1 CC3

- 011: событие Timer 2 CC2

- 100: событие Timer 3 TRGO

- 101: событие Timer 4 CC4

- 110: сигнал EXTI line 11

- 111: программный запуск SWSTART

Бит 15 JEXTTRIG. Разрешение внешнего запуска преобразования для инжектированных каналов.

Биты 14:12 JEXTSEL [2:0]. Выбор источника запуска для инжектированных каналов.

- 000: событие Timer 1 TRGO

- 001: событие Timer 1 CC4

- 010: событие Timer 2 TRGO

- 011: событие Timer 2 CC1

- 100: событие Timer 3 CC4

- 101: событие Timer 4 TRGO

- 110: сигнал EXTI line 15

- 111: программный запуск JSWSTART

Бит 11 ALIGN. Режим выравнивания результата преобразования по правому (0) или левому (1) краю.

Бит 8 DMA. Разрешение использования прямого доступа к памяти (DMA). Только для АЦП 1.

Бит 3 RSTCAL. Сброс калибровочных коэффициентов.

Бит 2 CAL . Запуск калибровки.

Бит 1 CONT. Разрешение режима непрерывного преобразования.

Бит 0 ADON . Разрешение работы модуля АЦП.

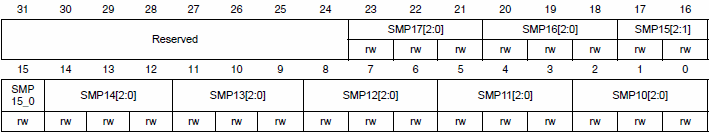

ADC_SMPR1 – регистр времени выборки каналов АЦП.

Биты 23:0 SMPx [2:0]. Время выборки канала

- 000: 1,5 цикла

- 001: 7,5 цикла

- 010: 13,5 цикла

- 011: 28,5 цикла

- 100: 41,5 цикла

- 101: 55,5 цикла

- 110: 71,5 цикла

- 111: 239,5 цикла

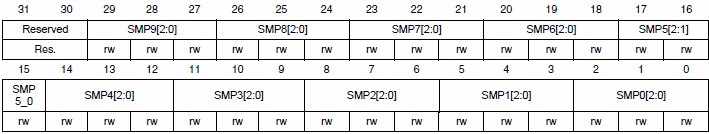

ADC_SMPR2 – регистр времени выборки каналов АЦП.

Биты 29:0 SMPx [2:0]. Время выборки канала

- 000: 1,5 цикла

- 001: 7,5 цикла

- 010: 13,5 цикла

- 011: 28,5 цикла

- 100: 41,5 цикла

- 101: 55,5 цикла

- 110: 71,5 цикла

- 111: 239,5 цикла

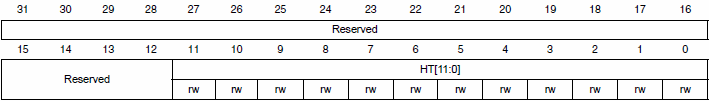

ADC_HTR – верхний порог оконного компаратора.

Биты 11:0 HT [11:0]. Верхний порог оконного компаратора.

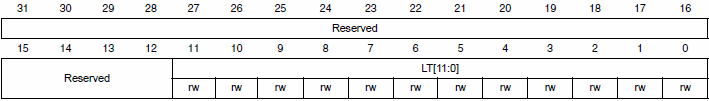

ADC_LTR – нижний порог оконного компаратора.

Биты 11:0 LT [11:0]. Нижний порог оконного компаратора.

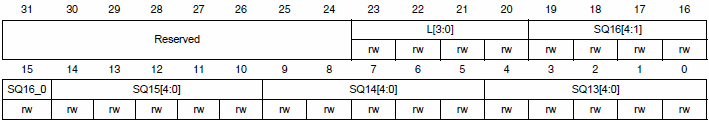

ADC_SQR1 – регистр последовательности опроса регулярных каналов.

Биты 23:20 L [3:0]. Количество регулярных каналов в цикле опроса.

- 0000: 1 преобразование;

- 00001: 2 преобразования;

- . . . . . . . . . . . . . . . . . . . . . . .

- 1111: 16 преобразований.

Биты 19:15 SQ16 [4:0]. Канал для 16го преобразования.

Биты 14:10 SQ15 [4:0]. Канал для 16го преобразования.

Биты 9:5 SQ14 [4:0]. Канал для 16го преобразования.

Биты 4:0 SQ13 [4:0]. Канал для 16го преобразования.

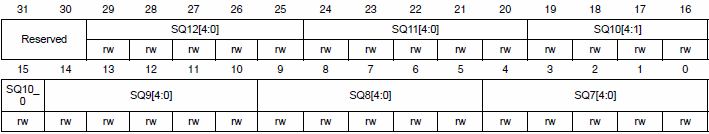

ADC_SQR2 – регистр последовательности регулярных каналов.

Биты 29:26 SQ12 [4:0]. Канал для 12го преобразования.

Биты 24:20 SQ11 [4:0]. Канал для 11го преобразования.

Биты 19:15 SQ10 [4:0]. Канал для 10го преобразования.

Биты 14:10 SQ9 [4:0]. Канал для 9го преобразования.

Биты 9:5 SQ8 [4:0]. Канал для 8го преобразования.

Биты 4:0 SQ7 [4:0]. Канал для 7го преобразования.

ADC_SQR3 – регистр последовательности регулярных каналов.

Биты 29:26 SQ6 [4:0]. Канал для 6го преобразования.

Биты 24:20 SQ5 [4:0]. Канал для 5го преобразования.

Биты 19:15 SQ4 [4:0]. Канал для 4го преобразования.

Биты 14:10 SQ3 [4:0]. Канал для 3го преобразования.

Биты 9:5 SQ2 [4:0]. Канал для 2го преобразования.

Биты 4:0 SQ1 [4:0]. Канал для 1го преобразования.

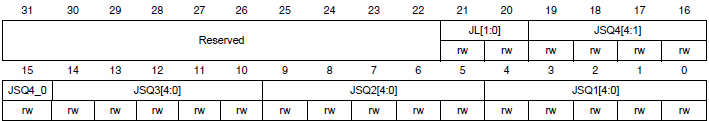

ADC_JSQR - регистр последовательности опроса инжектированных каналов.

Биты 21:20 JL [1:0]. Количество инжектированных каналов в цикле опроса.

- 00: 1 преобразование

- 01: 2 преобразования

- 10: 3 преобразования

- 11: 4 преобразования

Биты 19:15 JSQ4 [4:0]. Канал для 4го преобразования.

Биты 14:10 JSQ3 [4:0]. Канал для 3го преобразования.

Биты 9:5 JSQ2 [4:0]. Канал для 2го преобразования.

Биты 4:0 JSQ1 [4:0]. Канал для 1го преобразования.

В случае, если требуется опрашивать число каналов меньше 4, то биты JSQ смещаются в сторону старших разрядов.

| Поля регистра

ADC_JSQR |

Количество опросов | |||

| 1 | 2 | 3 | 4 | |

| JSQ4 | 1 преобразование | 2 преобразование | 3 преобразование | 4 преобразование |

| JSQ3 | 1 преобразование | 2 преобразование | 3 преобразование | |

| JSQ2 | 1 преобразование | 2 преобразование | ||

| JSQ1 | 1 преобразование | |||

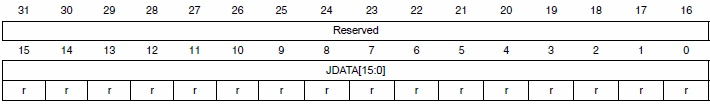

ADC_JDR1 - ADC_JDR4 – Результат преобразования инжекционных каналов.

Биты 15:0 JDATA[15:0]. Результат преобразования инжекционных каналов.

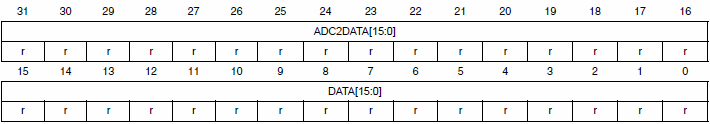

ADC_DR – результат преобразования регулярной группы.

Биты 31:16 ADC2DATA [15:0]. Результат преобразования АЦП 2. Только в режиме сдвоенных преобразований.

Биты 15:0 DATA [15:0]. Результат преобразований.

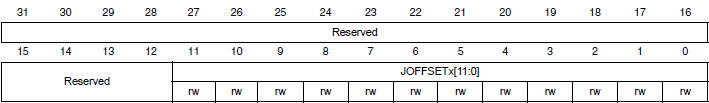

ADC_JOFR1-4 – регистр офсета результата инжектированных каналов.

Биты 11:0 JOFFSETx [11:0]. Значение офсета (смещения) результата преобразования инжектированных каналов.